"Eternity is a long time, especially towards the end: another short history of Moore's Law".

"I would have happily attributed the first part of the title of this editorial to Michel Audiard, only to learn that the author of this quote was none other than the Austro-Hungarian writer Franz Kafka. So you can set your reading level as high as you like, somewhere between the lightness of the former and the often sinister world of the latter.

Alternatively, a variation on this title could have been "No exponential is forever: but forever can be delayed", which was coined by Gordon Moore (Intel), the eponymous author of the law in question. But who enacted this law that everyone thinks they know but very few manage to spell out? Moore's Law is the story of the tremendous industrial revolution that began with the miniaturisation of integrated circuits, which today contain billions of transistors. It is also the law that governs the digitisation of our society. Here's a short history...

The origin of Moore's law

It is on the basis of a reduced set of data, whereas it was Fairchild employeethat G. Moore had empirically formulated around 1965that increasing the integration density by a factor of two at regular intervals minimises the manufacturing cost per unit transistor, with an additional gain in frequency performance. Starting with a 32-component integrated circuit in 1964, Moore came back to support his projection in 1975 at theMEI (a conference attended by a large industrial audience): a memory circuit with 65,000 transistors from Intel's production lines confirmed its prediction of exponential growth. It was against this backdrop that Moore's metronome began to beat, with a roadmap that brought into resonance the increase in integration density and performance, on the one hand, with the reduction in cost/bit, on the other.

It was around the same time that R. Dennard (IBM) theorised the rules of scaling ("scaling law") of the MOS transistor which demonstrated that its power density remained constant as its dimensions were reduced (and at the same operating frequency!). Dennard's work confirmed the promise of a doubling of the integration density and a gain in frequency of 40% for a homothetic reduction of √2 in the transistor's dimensions and an increase in the channel doping in the same proportion.

Elevated to the sacred rank of "technological "bibleMoore's Law became a self-fulfilling prophecy to which the semiconductor industry dedicated itself in order to anticipate the development of new processes and equipment, particularly lithography. Never before had an industrial sector had such a well-defined roadmap, with a trajectory setting out both the technical and economic rules of the game.

We knew where we were going without having all the keys to get there, but we were going! Aware of the challenges posed by the continuation of Moore's Law, the world semiconductor industry agreed in 1993 to formalise the ITRS roadmap (International Technology Roadmap for Semiconductors), which made it possible to set precise quantified objectives on a virtually irrevocable timetable. The first ITRS technology node positioned itself on a pattern size (the length of the gate in the first instance) of 0.5 μm, projected 300,000 gates per chip, anticipated 16 and 4 Megabit DRAM and SRAM memoriesrespectively, at a cost of 4$ per cm2! The regular interval, mentioned above, was now set at three years to progress from one technological node to the next.

The saga of Happy Scaling

For three decades, the global semiconductor industry enjoyed a long, quiet period of unprecedented growth, made possible by a simple reduction in the geometry of the single MOS transistor. But all things must come to an end! This period known as the Happy Scaling could almost be compared to the post-war "trente glorieuses" (thirty glorious years)... with a thirty-year time lag. Indeed, at the dawn of the 2000s, the first pitfalls in the simple geometric law of scaling A number of second-order physical effects were now coming to the fore: reduced carrier mobility with increasing channel doping, leakage of the SiO2-based gate oxide below 3 nm thickness, and parasitic depletion of the polysilicon gate.

The inventiveness of the industrial and academic microelectronics communities responded to this by creating, respectively use of technological boosters such as mechanical constraints, high-permittivity dielectrics and metal grids. A second major stumbling block emerged at the same time: although Dennard's rules stated that the energy consumed by an elementary gate is reduced by the scaling factor (reduction to the cube), heat dissipation now limited the clock frequency to around 3GHz. The solution to this challenge was to increase the number of microprocessor cores in order to favour parallel processing of binary operations.

Marked by the first hiccups in the irresistible progress of Moore's Law, the early 2000s was also a time of intense reflection, giving rise to two complementary paradigms: Beyond CMOS and More-than-Moore. The first is of fundamental importance, introducing in particular a break with the material of choice, silicon. It includes 360-degree research into devices, materials and information processing methods (tunnel FETs, spintronics, superconductivity, molecular electronics, graphene, carbon nanotube, chalcogenide, topological materials, photonics and optical computing, etc.). Despite the wealth of avenues investigated, it is no offence to this high-quality research to observe that none has supplanted silicon technologies. The second paradigm breaks with the logic of the race for size as the sole driver of growth and innovation. It involves integrating a wide variety of functions to form an autonomous system, either in a monolithic integration logic (System-on-Chip SoC, everything on the same silicon chip) or by favouring the heterogeneous integration of functions whose manufacturing constraints are incompatible (SiP System-in-Package).

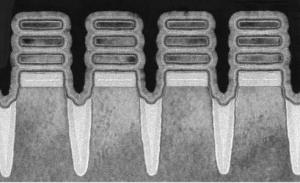

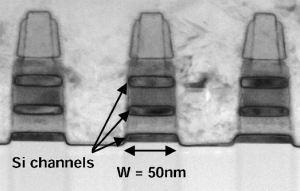

Despite his initial health problems, Moore's Law nevertheless continued to unfold, with the introduction of new innovations aimed at strengthening the transistor's electrostatic integrity, i.e. its ability to fully play its role as a switch without prohibitive leakage current in the blocked state. The silicon-on-insulator substrate (SOI, Silicon-on-Insulator) would reach the age of reason after 25 years of development, with the technical cost/benefit balance finally on the right side.. Numerous solutions relating to the architecture of the unitary transistor were proposed, all aiming to reinforce the control of the field effect by a gate encasing a thin and/or narrow channel. At the beginning of the 2010 decadeThe finned transistor architecture (FinFET) was the big winner in this revolution, which saw the planar transistor structure on a solid substrate relegated to the dustbin. Thanks to its conservative planar construction, the MOS FDSOI (Fully-Depleted SOI) pushed by STMicroelectronics continued to play a particularly interesting role as a runner-up, thanks to its rear grille control, which allowed it to modulate the fuel consumption/speed compromise as required.

Europe's penchant for More-than-Moore

There have been many articles predicting the end of Moore's Law for more than 20 years, for reasons that research and industry have swept aside. However, common sense leaves us in doubt when we observe that the critical dimensions of MOS technologies are flirting dangerously with the granularity of matter.

With a silicon lattice parameter of 0.543 nm, would this mean that the 2 nm node transistor unveiled by IBM in May 2021 has only 4 lattices? Already marked by quantisation effects, would the transistor's operation become completely quantum? Under these conditions, how can we control the variability introduced by the stochastic nature of the manufacturing stages? Would the transistor be vulnerable to a simple one-off defect?

Fortunately, these extremes have not been and will not be reached. This is because the technological node of 1993 and that of 2021 are not compared in the same way. With theintroduction of three-dimensional structures such as FinFETThe qualification of the node has moved from a geometric definition to a scale based on equivalence. For example, the 5nm FinFET node produced by Intel, Samsung or TSMC has a gate length of around 18nm, whereas the IRDS projections, which have been relaying the ITRS since 2015, show that the counter for the 0.7nm node will be stuck at 12nm in 2034!

Anecdotally, inspection of the figures opposite and below reveals an uncanny resemblance. For the 2nm node recently publicised by IBM-Research, these illustrations show that the keys to optimising transistors based on stacked nanoribbons and a coated gate had been perfectly identified in thesis work supported in 2009 as part of an STMicroelectronics CIFRE agreement.. This raises a legitimate question: why has this type of architecture, which has positioned itself as the successor to FinFET, not been pushed to the limit of its development in the European ecosystem? It will not have escaped your notice in the preceding list that the list of industrial competitors capable of sustaining the historic slope of Moore's Law is now down to two or three, whereas there were still ten of them in 2010-2012.

A major player in European microelectronics such as STMicroelectronics quickly realised that the road to diversification (More-than-Moore) enabled us to design more appropriate and effective solutions for specific needs and uses. An emblematic example is the automotive industry whose vehicles are crammed with electronic components (microcontrollers, radar, lidar, cameras, multimedia, cybersecurity, artificial intelligence, connectivity, power, etc.) ranging from 180 for the bottom of the range (Dacia) to more than 2,400 for the top of the range (Mercedes). As in many applications, cutting-edge 5nm technologies are not needed to optimise specialised functions.

Figures taken from Emilie Bernard's thesis, defended in Jan 2009 as part of a CIFRE STMicroelectronics thesis.

It is against this backdrop of diversification that IEMN has been working with STMicroelectronics since 2003 in a joint laboratory structure where four major themes are being developed:

1) Potential of silicon technologies for RF and millimetre wave, 2) Communicating systems and on-board artificial intelligence, 3) Small-scale metrology using high-frequency acoustics and 4) Functional packaging and microthermics. Our common goal is twofold: high scientific ambition and high industrial relevance. All of this with the secret hope, in all proportion and humility, ofmaking our contribution to the sovereignty of Europe's semiconductor industry, ...

To find out more, click here: If you are interested in a summary that provides a remarkably clear vision of the semiconductor industry, the Académie des technologies' dossier will provide you with many keys to understanding, particularly the European Commission's European Chips Act. ( https://www.academie-technologies.fr/publications/les-technologies-materielles-supports-du-numerique-futur-trois-questions/ )