Visite du Comité AERES

Seminar Dr. Gunther Roelkens 23/01/2014

« Heterogeneous silicon photonic integrated circuits for spectroscopic sensing and optical communication »

Gunther Roelkens received the PhD degree in engineering (photonics) at Ghent University, Belgium in 2007. He has been a research professor at Ghent University since 2010 working in the field of silicon photonics, more specifically mid-infrared silicon photonic integrated circuits, silicon nonlinear optics and III-V semiconductor integration on silicon photonic integrated circuits. He is also assistant professor at Eindhoven University of Technology, the Netherlands. The research highlights of his group are the first fully integrated short-wave infrared spectrometer chip, record nonlinear parametric gain on a silicon chip and high efficiency multi-wavelength lasers integrated on silicon waveguide circuits. Dr. Roelkens has authored and co-authored over 100 refereed journal publications

In this talk I will review our work on silicon photonic integrated circuits and the integration of other materials on top of the silicon waveguide circuits for applications in mid-infrared spectroscopic sensing and for telecom / datacom applications. This includes the integration of III-V semiconductors, colloidal nanoparticles and non-reciprocal materials on top of silicon-based waveguide circuits. The use of integrated nonlinear optical functionalities is also discussed.

Seminar Abderrahmane KADRI

« Les activités de recherche et de formation au Laboratoire LEMOP, Université d’Oran, Algérie

Initiation d’un projet de coopération sur les cellules photovoltaïques solaires InXGa1-XN/GaN »

Prof. KADRI Abderrahmane

Laboratoire d’Etude des Matériaux Optoélectronique et Polymères (L.E.M.O.P.)

Département de Physique, Faculté de Sciences Exactes et Appliquées, Université d’Oran, Algérie

21/11/2013 – Salle du conseil – IEMN

Résumé :

Dans cet exposé, je présenterai les activités de recherche et de formation au sein du Laboratoire d’Etude des Matériaux, Optoélectronique et Polymères (L.E.M.O.P.) à l’Université d’Oran en Algérie. Je présenterai plus particulièrement les activités de coopération de notre laboratoire, dont le projet de recherche en cours d’initiation avec l’équipe du Professeur N. ROLLAND et du Dr F. MEDJDOUB à l’I.E.M.N. C.N.R.S. sur les cellules photovoltaïques solaires à hétéro-structures p-i-n à Multi-puits Quantiques InXGa1-XN/GaN.

Seminar Prof. Ludger WIRTZ

Optical and vibrational properties of MoS2

Ludger WIRTZ

Physics and Materials Science research unit, University of Luxembourg

26/11/2013 à 11h00 – Salle du Conseil – IEMN

Following the hype on graphene, other layered materials are recently achieving a lot of attention.

One of them is molybdenum disulfide. Contrary to graphene, MoS2 has a band-gap of about 2 eV

and might thus be a suitable candidate for electronics and optics applications. I will give an

overview over the properties of the material and summarize the ongoing debate on the mobility of

the material. I will also present our own recent work on the phonon dispersion of of bulk and fewlayer

MoS2, where the origin of the anomalous Davydov splitting is still not ultimately clarified.

Furthermore, I will discuss the influence of excitonic effects and spin-orbit splitting on the optical

properties of MoS2.

Seminar Daniel MANDLER

« Chemistry and Electrochemistry in Two Dimensions: from Langmuir Blodgett Films to Monolayers and Polymeric Films »

Prof. Daniel MANDLER

Daniel.mandler@mail.huji.ac.il

Institut of Chemistry, The Hebrew University of Jerusalem, Israel

27/11/2013 à 14h00 – Salle du Conseil de l’IEMN

Electrochemistry deals with charge transfer across interfaces. As is well known, the structure of the interface affects very much charge transfer and therefore controlling and characterization the interface on a molecular level is of utmost importance.

The lecture will focus on different approaches for controlling the interface and its implications and applications in electrochemistry. These will include structuring the interface using Langmuir and Langmuir-Blodgett films, applying self-assembled monolayers and if time permits manipulating thin polymeric films. Different systems and applications will be presented; films at the water-air interface based on individual molecules, polymers and nano-objects. Applications of functionalized self-assembled monolayers as a means of selectively interacting with metal ions and organization of asymmetric nano-objects for future photocatalysis, will be described. Various characterization methods will also be discussed such as horizontal touching voltammetry and scanning electrochemical microscopy.

Séminaire du Groupe Physique

Characterization of Phosphorus Doped Silicon Nanocrystals Embedded in SiO2

October 17, 2013 – at 2pm – IEMN, LCI – Salle du Conseil

Presenter

Sebastian Gutsch – University of Freiburg

sebastian.gutsch@imtek.uni-freiburg.de

Abstract

Phosphorus (P) doped silicon nanocrystals (Si NCs) are prepared by deposition and annealing of P doped silicon-rich oxide / silicon oxide (SiO2) multilayers. The chemical environment of P is determined from X-ray photoelectron and X-ray absorption near edge spectroscopy. It is found that P is incorporated into the Si NCs down to diameters of about 2.5 nm. However, the results suggest that essentially no free electrons are generated in this doping process. Using atom probe tomography, it is further found that large amounts of the dopants segregate at the Si NC / SiO2 interface. In addition, photoluminescence spectroscopy and electrical characterization of the multilayers indicate that the majority of incorporated P atoms have only a small impact on the optical and electronic properties. It is shown that less than 1% of the doped P atoms occupy a substituitional site and that the donor ionization energy significantly exceeds kT at room temperature.

Secondes Journées Franco libanaises (brèves)

Trois universités régionales (Lille 1, UVHC et ULCO) en partenariat avec l’Université Libanaise et tous les partenaires de l’ARCUS E2D2 organisent du 22 au 25 octobre 2013 « Les Secondes Journées Franco-Libanaises ».

>> En savoir plus

Secondes journées Franco-Libanaises JFL2 : Avancées de la Recherche et de ses Applications

Du 22 au 25 octobre 2013 – ULCO Côte d’Opale

Du 22 au 25 octobre 2013 – ULCO Côte d’Opale

Dans le but de créer un réseau de collaborations regroupant les principales disciplines scientifiques au sein d’un groupement de recherche international, trois universités régionales (Lille 1, UVHC et ULCO) en partenariat avec l’Université Libanaise et tous les partenaires de l’ARCUS E2D2 organisent du 22 au 25 octobre 2013 « Les Secondes Journées Franco-Libanaises ».

L’un des objectifs principaux est de renforcer les actions en cours, principalement celles qui ont conduit ou peuvent conduire à des thèses en cotutelle. Développer des formations sous forme de masters en double diplôme et initier l’émergence d’équipes de recherche regroupant les principaux partenaires au sein de groupes de recherche internationaux. Avec la participation des laboratoires de recherche : IEMN DOAE, CALHISTE, LAMAV, LMCPA.

Cinq sessions sont prévues, illustrant chacune les grandes thématiques des différents laboratoires libanais, français et autres partenaires (Maroc et Palestine). Dans chaque session, des conférences sélectionnées par le comité scientifique seront données par des représentants des laboratoires participants et des invités. A l’issue de chaque session, une séance de posters est prévue afin de donner l’occasion au plus grand nombre de participants d’exposer leurs travaux.

Des visites des Maisons de Recherche dans les différents sites de l’ULCO (Dunkerque – Calais – Boulogne sur Mer) seront également proposées.

- Session 1 : Aménagement et Développement Durable

- Session 2 : Infrastructures et Systèmes Complexes

- Session 3 : Expertise et Traitement en Environnement

- Session 4 : Optique, Lasers, Interface Physique–Biologie Session 5 : Table Ronde ARCUS E2D2

Contacts Pr Edmond ABI-AAD edmond.abiaad@univ-littoral.fr

Pr Antonio KHOURY akhoury@ul.edu.lb

Inscriptions : www.jflpi.fr

Zero-dimensional transistor harvests bubble energy wasted during water electrolysis

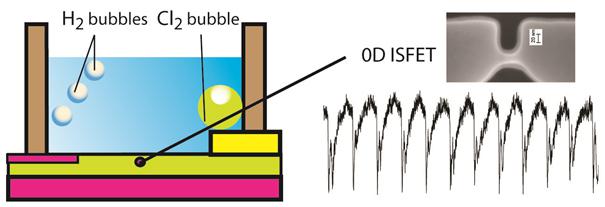

A zero-dimensional transistor is placed in contact with a water droplet containing NaCl ions. A current between the anode and cathode generates hydrogen and chlorine bubbles, which the transistor can detect and transform into electric pulses. N. Clément et al. © American Chemical Society

When hydrogen is produced from water during electrolysis, some energy is lost at each bubble emission. In a new study, researchers from the Institut for Electronics Microelectronics and Nanotechnology (CNRS/Univ. of Lille), NTT, Tokyo and CEA Marcoules have demonstrated that 25-nm transistors — so small that they are considered zero-dimensional (0D) — can be used to transform this lost energy into electric pulses. Millions of these 0D transistors could be used to detect individual bubbles and generate electric pulses at an optimal efficiency, gathering part of the energy lost during electrolysis and making it available for other uses. In theory, 2 million 0D transistors could fit below the microbath, which results in an output pulse power of 500 µW and a pulse power efficiency of about 99%.

These results could have a variety of applications, such as lab-on-chip devices for hydrogen emission. Another potential application is in physiology, since the electric signal has a similar amplitude as that of the action potential in a neuron.

This paper was published in Nanoletters : Water Electrolysis and Energy Harvesting with Zero-Dimensional Ion-Sensitive Field-Effect Transistors. N. Clément, K. Nishiguchi, J.F. Dufrêche, D. Guérin, A.Fujiwara & D. Vuillaume. Nano Letters 13(8), 3903-3908 (2013), http://dx.doi.org/10.1021/nl4019879

Contact : N. Clément (nicolas.clement@iemn.univ-lille1.fr / 03 20 19 79 32)