« L’éternité, c’est long, surtout vers la fin : une autre histoire courte de la loi de Moore »

« J’aurais volontiers attribué la première partie du titre de cet édito à Michel Audiard avant d’apprendre que l’auteur de cette citation n’est autre que l’écrivain austro-hongrois Franz Kafka. Vous placerez donc votre niveau de lecture à la hauteur que vous souhaitez, quelque part entre la légèreté du premier et l’univers souvent sinistre du second.

Alternativement, une variation de ce titre aurait pu être « No exponential is forever: but forever can be delayed » dont la paternité revient à Gordon Moore (Intel), auteur éponyme de la loi dont il est ici question. » Mais qui a édicté cette loi que tout le monde croit connaitre mais que bien peu parviennent à en énoncer le contenu ? La loi de Moore, c’est l’histoire de la formidable révolution industrielle dont l’origine se trouve dans la miniaturisation des circuits intégrés embarquant aujourd’hui des milliards de transistors. C’est aussi elle qui préside à la numérisation de notre société. En voici une histoire courte…

À l’origine de la loi Moore

C’est sur la base d’un jeu réduit de données, alors qu’il était employé de Fairchild, que G. Moore avait empiriquement formulé vers 1965, que l’augmentation de la densité d’intégration d’un facteur deux à intervalle régulier permettrait de minimiser le coût de fabrication par transistor unitaire avec de surcroît un gain de performance en fréquence. Partant d’un circuit intégré de 32 composants en 1964, Moore revint étayer sa projection en 1975 à l’IEDM (conférence pilotée par une forte audience industrielle) : un circuit mémoire de 65000 transistors issu des lignes de fabrication d’Intel venait confirmer sa prédiction de croissance exponentielle. C’est dans ce contexte que le métronome de Moore se mettait à battre avec une feuille de route faisant rentrer en résonance l’accroissement de la densité d’intégration et des performances, d’une part, avec la réduction du coût/bit, d’autre part.

C’est à la même époque que R. Dennard (IBM) théorisa les règles de mise à l’échelle (« scaling law ») du transistor MOS qui démontrait que sa densité de puissance restait constante avec la réduction de ses dimensions (et à fréquence d’opération identique !). Les travaux de Dennard confirmaient la promesse d’un doublement de la densité d’intégration et d’un gain en fréquence de 40% pour une réduction homothétique de √2 des dimensions du transistor et le rehaussement du dopage canal dans la même proportion.

Élevée au rang sacré de « bible » technologique, la loi de Moore devint dès lors une prophétie auto-réalisatrice à laquelle l’industrie du semiconducteur se voua pour anticiper le développement de nouveaux procédés et la mise au point de nouveaux équipements, en particulier ceux de lithographie. Jamais une filière industrielle n’avait eu une feuille de route aussi bien tracée selon une trajectoire fixant à la fois les règles du jeu technique et économique.

Le chemin comportait de nombreux défis et verrous technologiques : on savait où on allait sans toutefois détenir toutes les clefs pour s’y rendre, mais on y allait ! Consciente des enjeux posés par la poursuite de la loi de Moore, l’industrie mondiale du semiconducteur s’accorda en 1993 pour formaliser la feuille de route ITRS (International Technology Roadmap for Semiconductors) qui permit de fixer des objectifs quantifiés précis sur un calendrier quasi-irrévocable. Ainsi le premier nœud technologique de l’ITRS se positionnait sur une taille de motif (la longueur de grille en première intention) de 0.5 μm, projetait 300000 portes par puces, anticipait des mémoires DRAM et SRAM de 16 et 4 Mégabits, respectivement, le tout pour un coût de 4$ par cm2 ! L’intervalle régulier, évoqué plus haut, était dorénavant fixé à trois ans pour progresser d’un noeud technologique au suivant.

La saga du Happy Scaling

Pendant trois décennies, la filière mondiale des semiconducteurs connut ainsi le parcours d’un long fleuve tranquille avec une croissance sans précédent rendue possible par la simple réduction de géométrie du transistor MOS unitaire. Mais tout a une fin ! Cette période dite du Happy Scaling pourrait presque s’apparenter aux trente glorieuses de l’après-guerre, … avec trente ans de décalage. En effet, à l’orée des années 2000, les premiers écueils à la simple loi géométrique de scaling se firent jour avec une accumulation d’effets physique du second ordre qui prenaient désormais le devant de la scène : réduction de la mobilité des porteurs avec le niveau de dopage du canal, fuite de l’oxyde de grille à base de SiO2 sous 3 nm d’épaisseur, déplétion parasite de la grille de polysilicium.

Ce à quoi l’inventivité de la communauté industrielle et académique de la microélectronique répondit, respectivement, par la mise en oeuvre de boosters technologiques que sont les contraintes mécaniques, les diélectriques à haute permittivité et les grilles métalliques. Un second écueil de taille se fit jour à la même époque : même si les règles de Dennard exprimaient que l’énergie consommée par une porte élémentaire est réduite par le facteur de scaling (réduction au cube), la dissipation de chaleur limitait désormais la fréquence d’horloge aux alentours de 3GHz. La solution à ce défi fut d’augmenter le nombre de cœurs des microprocesseurs afin de privilégier le traitement parallèle des opérations binaires.

Marqué par les premiers accrocs au déroulement irrésistible de la loi de Moore, le début des années 2000 fut également l’instant d’une intense période de réflexion donnant naissance à deux paradigmes complémentaires : Beyond CMOS et More-than-Moore. Le premier revêt un caractère fondamental en introduisant notamment une rupture avec le matériau de prédilection qu’est le silicium. On y retrouve des recherches à 360 degrés sur les dispositifs, les matériaux et les méthodes de traitement de l’information (FETs tunnel, spintronics, superconductivité, électronique moléculaire, graphène, nanotube de carbone, chalcogénure, matériaux topologiques, photonique et calcul optique, …). Malgré la très grande richesse des pistes investiguées, ce n’est pas faire offense à cette recherche de qualité que d’observer qu’aucune n’a supplanté les technologies silicium. Le second paradigme casse la logique de la course aux dimensions comme unique relais de croissance et d’innovation. Il consiste à intégrer une grande variété de fonctions constituant un système autonome, soit dans une logique d’intégration monolithique (SoC System-on-Chip, tout sur la même puce de silicum) soit en privilégiant l’intégration hétérogène de fonctions dont les contraintes de fabrications sont incompatibles (SiP System-in-Package).

Malgré ses premiers ennuis de santé, la loi de Moore continuait néanmoins à se dérouler avec l’introduction de nouvelles innovations dont l’objectif était de renforcer l’intégrité électrostatique du transistor, à savoir, sa capacité à jouer pleinement son rôle d’interrupteur sans courant de fuite prohibitif à l’état bloqué. Le substrat silicium-sur-isolant (SOI, Silicon-on-Insulator) allait ainsi atteindre son âge de raison après 25 ans de développement, la balance coût/bénéfice technique penchant enfin du bon côté. De nombreuses solutions touchant à l’architecture du transistor unitaire furent proposées, toutes visant à renforcer le contrôle de l’effet de champ par une grille enrobant un canal fin et/ou étroit. Au début de la décennie 2010, l’architecture de transistors à ailettes (FinFET) fut la grande gagnante de cette révolution qui passait aux oubliettes la structure de transistor planaire sur substrat massif. De par sa construction planaire conservative, la MOS FDSOI (Fully-Depleted SOI) poussée par STMicroelectronics continuait de jouer un rôle d’accessit particulièrement intéressant de par sa commande de grille arrière lui permettant de moduler à la demande le compromis consommation-vitesse.

L’inclination de l’Europe pour More-than-Moore

Nombreux furent les articles prédisant la fin de la loi de Moore et ce depuis plus de 20 ans pour raison que la recherche et l’industrie ont balayé. Le bon sens laisse néanmoins planer le doute en observant que les dimensions critiques des technologies MOS flirtent dangereusement avec la granularité de la matière.

Avec un paramètre de maille du silicium de 0.543 nm, cela voudrait-il dire que le transistor du nœud 2 nm dévoilé par IBM en mai 2021 ne comporte que 4 mailles ? Déjà marqué par des effets de quantification, le fonctionnement du transistor deviendrait-il complètement quantique ? Comment contrôler dans ces conditions, la variabilité introduite par la nature stochastique des étapes de fabrication ? Le transistor serait-il vulnérable face à un simple défaut ponctuel ?

Bien heureusement, ces extrémités ne sont pas atteintes et ne le seront pas. La raison en est que l’on ne compare pas le nœud technologique de 1993 avec celui de 2021 de la même manière. Avec l’introduction des structures tridimensionnelles telles que le FinFET, la qualification du nœud est passé d’une définition géométrique à une échelle par équivalence. Ainsi le nœud FinFET 5 nm industrialisé par Intel, Samsung ou TSMC affiche une longueur de grille de l’ordre de 18 nm alors que les projections de l’IRDS, qui relayent l’ITRS depuis 2015, révèle un compteur bloqué à 12 nm pour le nœud 0.7 nm en 2034 !

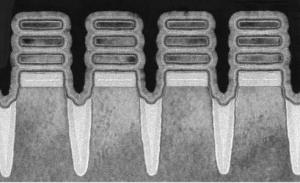

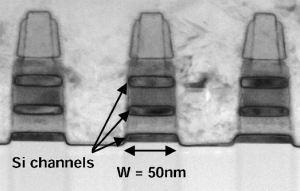

De manière anecdotique, l’inspection des figures ci-contre et ci-dessous révèlent une ressemblance troublante. Pour le nœud 2 nm récemment médiatisé par IBM-Research, ces illustrations démontrent que les clefs d’optimisation de transistors à base de nanorubans empilés et à grille enrobante avaient parfaitement été identifiés dans des travaux de thèse soutenus en 2009 dans le cadre d’une convention CIFRE STMicroelectronics. Dès lors, une question légitime s’impose à nous : pourquoi ce type d’architecture qui s’est positionné comme le successeur du FinFET n’a-t-il pas été poussé au bout de ses développements dans l’écosystème européen ? Le détail ne vous aura pas échappé dans l’énumération précédente que la liste des compétiteurs industriels capables de soutenir la pente historique de la loi de Moore sont aujourd’hui réduits à deux ou trois alors qu’ils étaient encore au nombre de dix en 2010-2012.

Un acteur majeur de la microélectronique européenne tel que STMicroelectronics a très rapidement réalisé que le chemin de la diversification (More-than-Moore) permettait de concevoir des solutions plus adaptées et performantes pour des besoins spécifiques et usages particuliers. Un exemple emblématique est celui de l’industrie de l’automobile dont les véhicules sont gavés de composants électroniques (microcontrôleurs, radars, lidars, caméras, multimédia, cybersécurité, intelligence artificielle, connectivité, puissance, …) de 180 pour le bas de gamme (Dacia) à plus de 2400 pour le haut de gamme (Mercedes). Comme dans beaucoup d’applications, les technologies 5 nm de pointe ne sont pas nécessaires pour optimiser des fonctions spécialisées.

Figures extraites de la thèse d’Emilie Bernard soutenue en Jan 2009 dans le cadre d’une thèse CIFRE STMicroelectronics

C’est dans ce contexte de diversification que l’IEMN accompagne STMicroelectronics depuis 2003 dans une structure de Laboratoire Commun où sont développés quatre thèmes majeurs :

1) Potentiel des technologies silicium pour la RF et le millimétrique, 2) Systèmes communicants et intelligence artificielle embarquée, 3) Métrologie à petite échelle par acoustique haute fréquence et 4) Packaging fonctionnel et microthermique. Notre objectif commun est double : une ambition scientifique élevée et une très grande pertinence industrielle. Le tout avec le secret espoir, toute proportion gardée et en restant humblement à notre place, d’apporter notre pierre à l’édifice de la souveraineté de l’Europe des semiconducteurs, …

Pour en savoir plus : si vous êtes intéressé(e) par une synthèse dressant une vision remarquablement limpide de l’industrie du semiconducteur, le dossier de l’Académie des technologies vous apportera de nombreuses clefs de compréhension, en particulier sur le European Chips Act de la Commission Européenne. ( https://www.academie-technologies.fr/publications/les-technologies-materielles-supports-du-numerique-futur-trois-questions/ )